# 極微小デバイスへの放射線照射損傷機構の解明 2 MeV electron irradiation effect of n-SOI gate-all-around nanowire FETs

高倉健一郎, 角田功, 米岡将士 Kenichiro Takakura, Isao Tsunoda, Masashi Yoneoka National Institute of Technology, Kumamoto College

#### Abstract

Input and output characteristics of n-channel SOI gate-all-around nanowire field-effect-transistors (SOI nGAANWFETs) evaluated. Device parameters as transconductance  $(g_m)$ , threshold voltage  $(V_T)$ , subthreshold swing (S) and drain induced barrier lowering (DIBL) are used for evaluation. The FET parameters as  $V_T$  and DIBL change suggest influence of gate shortening, but input/output characteristics do not infer remarkable. After the 2 MeV electron irradiation, drain current (I<sub>D</sub>) decreased. Degree of I<sub>D</sub> degradation by 2 MeV electron irradiation evaluated using gm and S, these are differed by gate width and length of the device. The gm and S degradation for a wide device of the gate width was remarkable. It can be concluded that when the device size became small, radiation tolerance increased, because of influence from buried oxide layer which lied under the nanowire-gate degradation by 2 MeV electron irradiation.

Keyword: Gate-all-around FET, electron irradiation, radiation tolerance

#### 1. Introduction

Multiple gate devices were considered as an alternative for planar complementary metal oxide semiconductor (CMOS) scaling [1]. FinFET is a most popular structure, which have a fin-gate structure have shown superior short-channel effect control [1, 2]. Nowadays, for 28 nm and below CMOS technologies there is a competition between planar fully depleted Silicon-on-Insulator (SOI) devices and FinFETs. FinFETs can be fabricated on either bulk silicon or SOI substrates. After a decade of extensive research with the efforts to improve and study the device performance, the main semiconductor industries have been investing in this technology. Apart from FinFET structures, various structures and/or materials have been demonstrated for the 20-nm node and beyond. Ultra-thin body and buried oxide (BOX) and gate-all-around (GAA) devices with the gate fully wrapped around the device body promising candidates for the next generation technology nodes. The BOX, such as FD SOI has significantly improved the threshold voltage (V<sub>T</sub>) variability and minimizing the short-channel effect [3].

The scaling of CMOS technologies leads to an intrinsic hardening against certain radiation effects, like Total Ionising Dose (TID) damage, so that the implementation of commercial-of-the-shelf ULSI components and circuits for harsh environments is becoming more popular [4-6]. This has been driven by multiple factors, including the implementation of microelectronics components and circuits in nuclear plants, high energy particle accelerators and artificial satellites. At the same time, this can eliminate the possible impact of radiation-induced trapped charges in the BOX layer or at the Si/BOX interface, so that high total-dose hardness is anticipated [7].

In this study, an electric characteristic of the SOI nGAA nanowire (NW) FETs such as short channel effect by reduction of device scales and degradation of input and output characteristics before and after irradiated 2 MeV electrons are investigated. Especially, radiation tolerance compared to the attention of gate width and length.

#### 2. Experimental Mechod

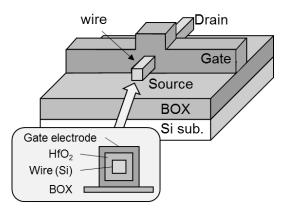

Figure 1 shows a studied device structure of a SOI n-channel GAANWFET [8]. Devices were processed on SOI substrates. For junction less devices, channel doping was obtained via ion implantation. This was followed by a spike anneal, after which device processing continued according to the baseline flow sequence dummy-gate electrode deposition (a-Si). The gate stack used in all devices was obtained by a replacement Metal Gate (RMG) high-k process and it consists of: an interfacial layer-SiO<sub>2</sub> formed by O<sub>3</sub>-oxidation and a high-k dielectric (HfO<sub>2</sub>) grown by atomic layer deposition, followed by the effective work function-metal and tungsten as the fill-metal. S/D silicide was done after the RMG module by opening vias through the stack, landing on the S/D areas. The device parameters of gate lengths (L) and widths (W) are listed in Table 1.

### [17017]

Figure 1. Device structure of the SOI nGAANWFET. Nano wire is surrounded by gate electrode.

In this study, damage of the electrical properties by 2 MeV electrons irradiation of SOI nGAANWFETs is investigated. Devices without applied bias voltage were irradiated at room temperature by 2 MeV electrons in the electron accelerator at the Takasaki QST. The electron fluence varied from  $1 \times 10^{14}$  to  $1 \times 10^{16}$  e/cm<sup>2</sup>. Input and output characteristics of SOI nGANWFET were measured before and after the 2 MeV electron irradiation using Keysight Technology B1500A device parameter analyzer.

Table 1. The list of gate length and width of the SOI nGAANWFETs.

| Device # | gate length | gate width | L/W  |

|----------|-------------|------------|------|

|          | L(nm)       | W(nm)      |      |

| E24T7    | 250         | 1000       | 0.25 |

| E24T8    | 450         | 1000       | 0.45 |

| E24T9    | 1000        | 1000       | 1.0  |

| E23T9    | 1000        | 130        | 7.8  |

| E22T10   | 1000        | 40         | 25   |

#### 3. Results and Discussion

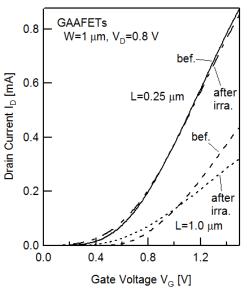

Figure 2 shows the input characteristics of the devices of E24T7 (L and W = 0.25 and 1.0  $\mu$ m) and E24T9 (L=1.0/W=1.0  $\mu$ m) before and after the 2 MeV electron irradiation (1×10<sup>16</sup> e/cm<sup>2</sup>). The drain current (I<sub>D</sub>) increased and VT shifts negative by gate length shorting. After the electron irradiation, it can be confirmed that I<sub>D</sub> decrease and V<sub>T</sub> negative shift. These electrical properties change by electron irradiation are smaller than general planer FETs [9].

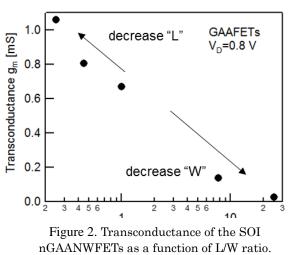

Electrical characteristics of SOI nGAANWFETs for before irradiation were studied. Figure 3 shows transconductance  $(g_m)$  of the devices against with the gate length and width (L/W) ratio. There are some combination of L and W for used device, to arrange with conductance of device from low one to high one, the L/W

Figure 2. Input characteristics of the SOI nGAANWFETs before and after 2 MeV electron irradiation ( $1 \times 10^{16}$  e/cm<sup>2</sup>). Gate length is L = 0.25 and 1.0 µm.

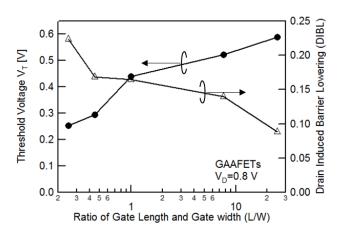

ratio introduce for evaluation. Correspondence of device number and L/W ratio listed in Table 1. In the case of L/W=1, it is largest device of our use (E24T9, L=1.0/W=1.0  $\mu$ m). When gate length decrease, the gm goes to the left side, and when gate width decrease, the gm goes to the right side. From Fig. 3, it can be said that gm change simply corresponds to the physical structure of gate. On the other hand, the short channel effect is concerned for the FETs which gate length became short. To evaluate this problem, V<sub>T</sub> and drain induced barrier lowering (DIBL) which determined by eq. (1) [10],

$$\text{DIBL} = \frac{V_T (V_D = 0.1 V) - V_T (V_D = 0.8 V)}{0.8 V - 0.1 V} \tag{1}$$

### [17017]

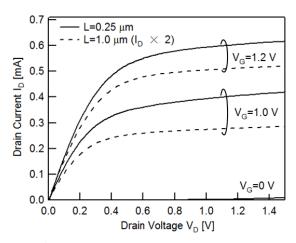

plotted with L/W ratio are shown in Figure 4. When the L becomes short, the L/W increase, and the  $V_T$  decreased and the DIBL increased. These suggest that short channel effect revealed with short L devices. However, drain current of output characteristics influence of short channel effect to the device operation seems small. Figure 5 compare output characteristics of the devices of short L (E24T7, L=0.25  $\mu$ m) and long L (E24T9, L=1.0  $\mu$ m). Both of I<sub>D</sub> for saturation region slightly increased with increase of V<sub>D</sub>. Compare with both characteristics, it can be say that no remarkable increase of slope at saturation region. In this case, device scale down is no significant inferred to the short channel effect of SOI nGAANWFETs.

Next, electrical characteristics degradation of the SIO nGAANWFETs by 2 MeV electrons discussed. As shown in Fig. 2, it is no significant decrease of  $I_D$  for E24T7 after  $1 \times 10^{16}$  e/cm<sup>2</sup> electron irradiation, while  $I_D$  for E24T9 decreased. It seems that the FETs in short gate length are higher radiation gm than that of long one. To

Figure 4. Device structure (L/W) dependence of threshold voltage (V<sub>T</sub>) and drain induced barrier lowering (DIBL) before 2 MeV electron irradiation.

Figure 5. Output characteristics of the SOI nGAANWFETs for gate length of L = 0.25 and 1.0  $\mbox{$\mu$m}.$

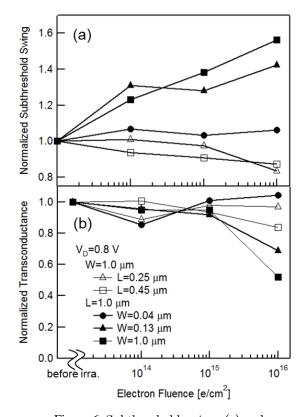

Figure 6. Subthreshold swings (a) and transconductances (b) of the SOI nGAANWFETs as a function of 2 MeV electron fluence. These are normalized using the value of before irradiation.

compare I<sub>D</sub> degradation degree by electron irradiation with the parameter of gate width and lengths subthreshold swings (S) and gms normalized by the value of before electron irradiation are shown in Figure 6. For the devices of L=0.25 µm which is shorter one and of W=0.04 µm narrower one, S and gm do not change largely at  $1 \times 10^{16}$  e/cm<sup>2</sup> electron irradiation. In contrast, gm changes remarkable, when L and W becomes long and wide, respectively. For the L=1.0/W=1.0 µm device, gm was decreased 50% compared to before irradiation. It pays attention to device structure, differences of radiation tolerance were considered. The nanowire gate which surrounded gate oxide fabricated on the BOX. It had been reported about subthreshold swing inferred by charge accumulation of BOX layer and it changes gate width [11]. Also, it is well known that charges accumulated in the oxide bulk and interface by radiation, and it inferred input and output characteristics of FET [12, 13]. In this case, influence of electron irradiation induced charge at BOX to the wider gate device larger than that of narrower one.

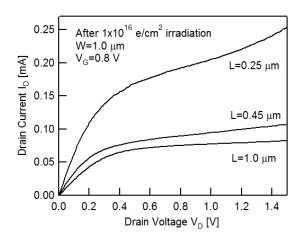

Figure 7 shows the output characteristics of  $1 \times 10^{16}$  e/cm<sup>2</sup> electron irradiated nGAANWFETs. For the device of L=1.0  $\mu$ m, gm and DIBL degraded by electron irradiation, though slope of saturation region does not

Figure 7. Output characteristics of the SOI nGAANWFETs after 2 MeV electron irradiation  $(1 \times 10^{16} \text{ e/cm}^2)$ . Gate widths are fixed W=1.0 µm, and gate lengths are L = 0.25, 0.45 and 1.0 µm.

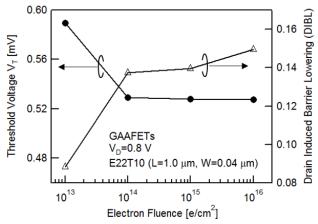

Figure 8. Threshold voltage (V<sub>T</sub>) and drain induced barrier lowering (DIBL) changes for the device of E22T10 (W=1.0/L=0.25  $\mu$ m) before and after 2 MeV electron irradiation.

increase largely. In contrast, for the device of L=0.25  $\mu$ m, saturation region of output characteristic slope rises. Also, V<sub>T</sub> decreased and DIBL increased by electron irradiation as shown in Fig. 8. As discussed above, short channel effects of nGAANWFET are emphasized by electron irradiation.

#### 4. Conclusion

2 MeV electron irradiation influences of input and output characteristics for the n-channel SOI gate-all-around FETs were investigated. Device parameters of V<sub>T</sub>, gm, DIBL tendency are lined up by the ratio of gate length and gate width (L/W). There are no serious problems to the input and output characteristics by device size reduction as short channel effect. Radiation tolerance of the devices as a function of the gate size to the irradiation of 2 MeV electrons compared. It was revealed that radiation tolerance was high so that device size became small. Transconductance and

subthreshold swing do not degrade even electron fluence increased to  $1 \times 10^{16}$  e/cm<sup>2</sup>, while transconductance about 50 % decreased when the gate width became wider. The main degradation factor is considered by charge accumulation to the buried oxide under the nanowire-gate by electron irradiation. It can be concluded that the objected device which especially device size became small, has high radiation tolerance.

#### References

- T. Chiarella, L. Witters, A. Mercha, C. Kerner, M. Rakowski, C. Ortolland, L.-Å. Ragnarsson, B. Parvais, A. De Keersgieter, S. Kubicek, A. Redolfi, C. Vrancken, S. Brus, A. Lauwers, P. Absil, S. Biesemans, T. Hoffmann, Benchmarking SOI and bulk FinFET alternatives for PLANAR CMOS scaling succession, Solid-State Electron. 54(9), pp. 855-860 (2010).

- [2] H. Iwai, Future of nano CMOS technology, Solid-State Electron. 112, pp. 56-57 (2015).

- [3] P.R. Rao, X. Wang and A.J.P. Theuwissen, Degradation of CMOS image sensors in deep-submicron technology due to γ-irradiation, Solid-State Electron. 52, pp. 1407-1413 (2008).

- [4] H.J. Barnaby, M. McLain and I.S. Esqueda, Total-ionizing-dose effects on isolation oxides in modern CMOS technologies, Nucl. Instr. and Methods B, 261, pp. 1142-1145 (2007).

- [5] H.L. Hughes and J.M. Benedetto, Radiation effects and hardening of MOS technology: devices and circuits, IEEE Trans. Nucl. Sci., 50, pp. 500-521 (2003).

- [6] A. Veloso, M.J. Cho, E. Simoen, G. Hellings, P. Matagne, N. Collaert and A. Thean, Gate-all-around NWFETs vs. triple-gate FinFETs: Junctionless vs. extensionless and conventional junction devices with controlled EWF modulation for multi-VT CMOS, proceedings of 2015 symposium on VLSI Technology, Kyoto, Japan, 16-18 June, pp.T138-T139.

- [7] T. Mizumo, J. Okumura, and A. Toriumi, Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET's, IEEE Trans. Electron Dev., 41, pp.2216-2221 (1994).

- [8] F. Andrieu, O.Weber, C. Fenouillet-Béranger, P. Perreau, J. Mazurier, T. Benoist, O. Rozeau, T. Poiroux, M. Vinet, L. Grenouillet, J.-P. Noel, N. Posseme, S. Barnola, F.Martin, C. Lapeyre, M. Cassé, X. Garros, M.-A. Jaud, O. Thomas,G. Cibrario, L. Tosti, L. Brevard, C. Tabone, P. Gaud, S. Barraud, T. Ernst, and S. Deleonibus, Planar Fully depleted SOI technology: A powerful architecture for the 20nm node and beyond, proceedings of International Electron Devices Meeting, San Francisco, California, USA, 6-8 December 2010, pp. 3.2.1-3.2.4.

- [9] H. Ohyama, K. Takakura, M. Yoneoka, K. Uemura, M. Motokia, K. Matsuoa, M. Araib, S. Kuboyama, E. Simoen, C. Claeys, Effect of gate interface on performance degradation of irradiated SiC-MESFET, Physica B, 401-402, pp. 37-40 (2007).

- [10] M. J. Deen and Z. X. Yan, DIBL in short-channel NMOS devices at 77 K, IEEE Transactions on Electron Devices, 39(4), pp. 908-915 (1992).

- [11] A. Es-Sakhi, M. Chowdhury, Analysis of device capacitance and subthreshold behavior of Tri-gate SOI FinFET, Microelectronics Journal, 62, pp. 30-37 (2017).

- [12] P.J. McWhorter, P.S. Winokur, Simple technique for separating the effects of interface traps and trapped-oxide

## [17017]

charge in metal-oxide-semiconductor transistors, Appl.

Phys. Lett., 48(2), pp.133-134 (1986).

[13] J.R. Schwank, M.R. Shaneyfelt, D.M. Fleetwood, J.A. Felix, P.E. Dodd, P. Paillet, V. Ferlet-Cavrois, Radiation Effects in MOS Oxides, IEEE Trans. Nucl. Sci., 55(4), pp. 1002 1002 1002 10000 1833-1853 (2008).